# Telecommunication Electronics

Alberto Tibaldi

March 14, 2011

# Contents

| 1        | Arc  | hitectures of radio systems                            | 4  |

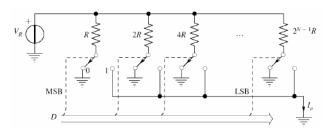

|----------|------|--------------------------------------------------------|----|

|          | 1.1  | Receiver                                               | 5  |

|          |      | 1.1.1 Heterodyne architecture                          | 5  |

|          |      | 1.1.2 Complex filters: SSB                             | 9  |

|          | 1.2  | Digital receivers                                      | 11 |

|          |      | 1.2.1 Digital architectures                            | 14 |

| <b>2</b> | Line | ear and non-linear use of bipolar junction transistors | 18 |

|          | 2.1  | Topology and biasing selection                         | 20 |

|          |      | 2.1.1 Biasing of the common emitter topology           | 21 |

|          | 2.2  | Analysis of the circuit                                | 24 |

|          |      | 2.2.1 Analysis of the bias point                       | 24 |

|          |      | 2.2.2 Bandwidth                                        | 25 |

|          | 2.3  | A design example                                       | 26 |

|          |      | 2.3.1 Resolution                                       | 26 |

|          | 2.4  | Non-linear issues on transistor amplifiers             | 29 |

|          |      | 2.4.1 Fight non-linearity : Compression                | 35 |

|          |      | 2.4.2 Fight non-linearity : Intermodulation            | 36 |

| 3        | App  | olications of non-linearity                            | 39 |

|          |      | 3.0.3 Amplifier with emitter resistance                | 41 |

|          | 3.1  | Tuned amplifiers                                       | 43 |

|          | 3.2  | Oscillators                                            | 47 |

|          |      | 3.2.1 Another technique for realizing oscillators      | 50 |

|          | 3.3  | Logarithmic Amplifier                                  | 51 |

|          |      | 3.3.1 Bipolar logarithmic amplifier                    | 57 |

|          |      | 3.3.2 Piecewise Approximation                          | 58 |

|          | 3.4  | Mixers and Multipliers                                 | 59 |

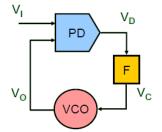

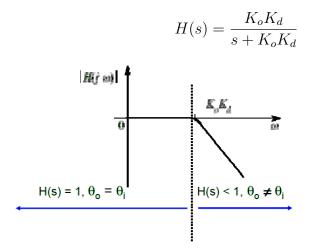

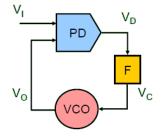

| <b>4</b> | Pha                                                       | se-lock loop 60                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6                                                                                 |

|----------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

|          | 4.1                                                       | Mathematical model of PLL                                                                                                                                                                                                                                                                                                                                                                                                                             | 6                                                                                 |

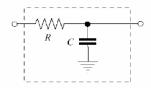

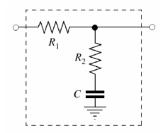

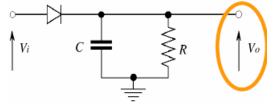

|          | 4.2                                                       | Loop filters                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                 |

|          |                                                           | 4.2.1 Steady state phase error                                                                                                                                                                                                                                                                                                                                                                                                                        | 3                                                                                 |

|          | 4.3                                                       | Phase detectors                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5                                                                                 |

|          |                                                           | 4.3.1 Analog phase detectors                                                                                                                                                                                                                                                                                                                                                                                                                          | 6                                                                                 |

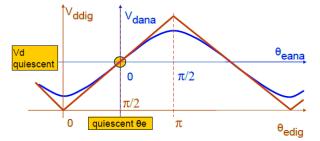

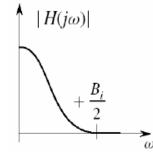

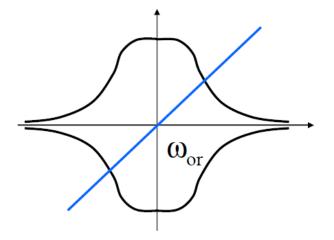

|          |                                                           | 4.3.2 Butterfly characteristic                                                                                                                                                                                                                                                                                                                                                                                                                        | 7                                                                                 |

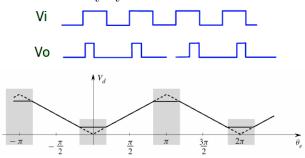

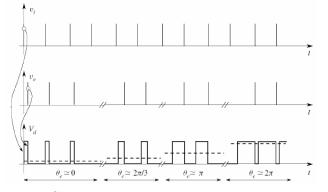

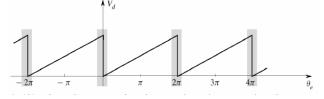

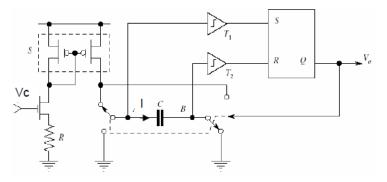

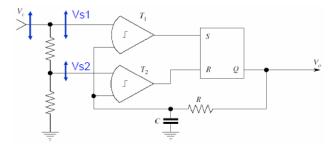

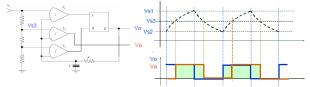

|          |                                                           | 4.3.3 Digital phase detectors                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                   |

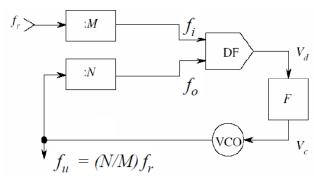

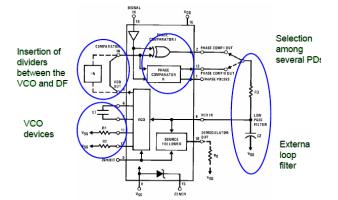

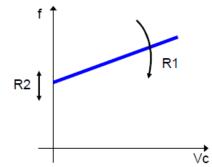

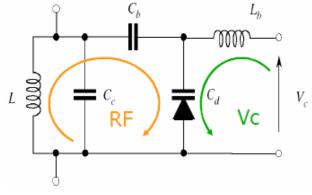

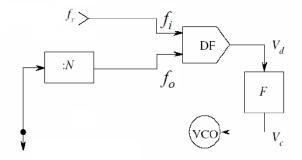

|          | 4.4                                                       | Signal synthesizers                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                   |

|          |                                                           | 4.4.1 Voltage Controlled Oscillators                                                                                                                                                                                                                                                                                                                                                                                                                  | 7                                                                                 |

|          |                                                           | 4.4.2 Fractional synthesizers                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                   |

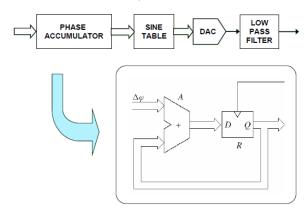

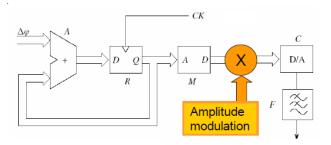

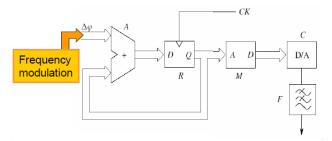

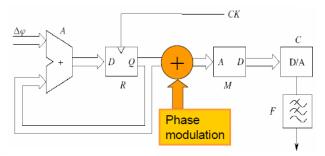

|          |                                                           | 4.4.3 Direct digital synthesis                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                   |

|          | 4.5                                                       | PLL as filter                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                   |

|          | 4.6                                                       | PLL as frequency demodulator                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                   |

|          |                                                           | 4.6.1 Coherent demodulation $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                    |                                                                                   |

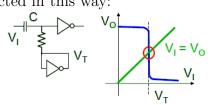

|          |                                                           | 4.6.2 Tone decoders $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                            | 5                                                                                 |

| <b>5</b> | <b>A</b>                                                  | log to Digital and Digital to Analog conversion 108                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                 |

| <u>n</u> | Ana                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ~                                                                                 |

| 0        |                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                   |

| 0        | 5.1                                                       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8                                                                                 |

| 0        |                                                           | Introduction       100         5.1.1       Sampling         Sampling       100                                                                                                                                                                                                                                                                                                                                                                        | 8<br>9                                                                            |

| 0        |                                                           | Introduction       104         5.1.1       Sampling       104         5.1.2       Quantization       114                                                                                                                                                                                                                                                                                                                                              | 8<br>9<br>4                                                                       |

| 0        | 5.1                                                       | Introduction       100         5.1.1       Sampling       100         5.1.2       Quantization       110         5.1.3       Signal conditioning       120                                                                                                                                                                                                                                                                                            | 8<br>9<br>4<br>0                                                                  |

| 0        |                                                           | Introduction       104         5.1.1       Sampling       104         5.1.2       Quantization       114         5.1.3       Signal conditioning       124         Digital to Analog Converters       124                                                                                                                                                                                                                                             | $8 \\ 9 \\ 4 \\ 0 \\ 1$                                                           |

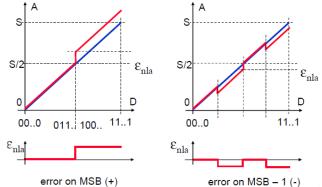

| 0        | 5.1                                                       | Introduction1005.1.1Sampling1005.1.2Quantization1105.1.3Signal conditioning120Digital to Analog Converters1205.2.1Quantifying of non-linear errors120                                                                                                                                                                                                                                                                                                 |                                                                                   |

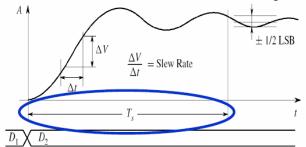

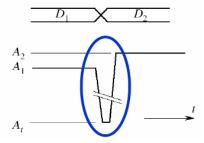

| 0        | 5.1                                                       | Introduction       104         5.1.1       Sampling       104         5.1.2       Quantization       104         5.1.3       Signal conditioning       114         5.1.3       Signal conditioning       124         Digital to Analog Converters       124         5.2.1       Quantifying of non-linear errors       124         5.2.2       Dynamic errors       124                                                                               |                                                                                   |

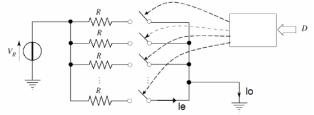

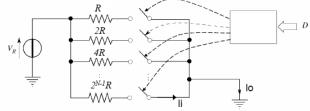

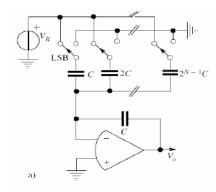

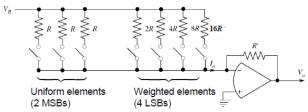

| 5        | 5.1<br>5.2                                                | Introduction1005.1.1Sampling1005.1.2Quantization1005.1.3Signal conditioning1105.1.3Signal conditioning120Digital to Analog Converters1205.2.1Quantifying of non-linear errors1205.2.2Dynamic errors1205.2.3Circuits for DAC120                                                                                                                                                                                                                        |                                                                                   |

| 0        | 5.1                                                       | Introduction1045.1.1Sampling1045.1.2Quantization1045.1.3Signal conditioning1145.1.3Signal conditioning124Digital to Analog Converters1245.2.1Quantifying of non-linear errors1245.2.2Dynamic errors1245.2.3Circuits for DAC124Analog to Digital Converters134                                                                                                                                                                                         | $     8 \\     9 \\     4 \\     0 \\     1 \\     3 \\     5 \\     6 \\     2 $ |

|          | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>             | Introduction1005.1.1Sampling1005.1.2Quantization1005.1.3Signal conditioning1145.1.3Signal conditioning120Digital to Analog Converters1205.2.1Quantifying of non-linear errors1205.2.2Dynamic errors1205.2.3Circuits for DAC120Analog to Digital Converters1305.3.1Static and Dynamic errors130                                                                                                                                                        | 8       9       4       0       1       3       5       6       2       3         |

|          | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul> | Introduction1005.1.1Sampling1005.1.2Quantization1105.1.3Signal conditioning1105.1.3Signal conditioning120Digital to Analog Converters1205.2.1Quantifying of non-linear errors1205.2.2Dynamic errors1205.2.3Circuits for DAC120Analog to Digital Converters1305.3.1Static and Dynamic errors130Circuital implementations130                                                                                                                            | 89401356234                                                                       |

|          | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>             | Introduction1005.1.1Sampling1005.1.2Quantization1105.1.3Signal conditioning112Digital to Analog Converters1205.2.1Quantifying of non-linear errors1205.2.2Dynamic errors1205.2.3Circuits for DAC120Analog to Digital Converters1305.3.1Static and Dynamic errors130Circuital implementations130Differential converters140                                                                                                                             | $8 \\ 9 \\ 4 \\ 0 \\ 1 \\ 3 \\ 5 \\ 6 \\ 2 \\ 3 \\ 4 \\ 0$                        |

|          | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul> | Introduction1005.1.1Sampling1005.1.2Quantization1105.1.3Signal conditioning120Digital to Analog Converters1205.2.1Quantifying of non-linear errors1205.2.2Dynamic errors1205.2.3Circuits for DAC120Analog to Digital Converters1305.3.1Static and Dynamic errors133Circuital implementations134Differential converters1405.5.1 $\Delta$ converters140                                                                                                 | 8940135623401                                                                     |

| 5        | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul> | Introduction100 $5.1.1$ Sampling100 $5.1.2$ Quantization110 $5.1.3$ Signal conditioning110 $5.1.3$ Signal conditioning120Digital to Analog Converters120 $5.2.1$ Quantifying of non-linear errors120 $5.2.2$ Dynamic errors120 $5.2.3$ Circuits for DAC120Analog to Digital Converters133 $5.3.1$ Static and Dynamic errors133Circuital implementations134Differential converters144 $5.5.1$ $\Delta$ converters144 $5.5.2$ Logarithmic converters144 | 89401356234017                                                                    |

| 5        | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>5.4</li></ul> | Introduction1005.1.1Sampling1005.1.2Quantization1105.1.3Signal conditioning120Digital to Analog Converters1205.2.1Quantifying of non-linear errors1205.2.2Dynamic errors1205.2.3Circuits for DAC120Analog to Digital Converters1305.3.1Static and Dynamic errors133Circuital implementations134Differential converters1405.5.1 $\Delta$ converters140                                                                                                 | 894013562340171                                                                   |

# Introduction

These text is the transcription of the notes, taken by the author, from the "Telecommunication Electronics" lectures, held by Professor Dante Del Corso in "Politecnico di Torino", academic year 2009/2010.

All the images of this text were taken from the learning material of the course, prepared by the Professor, under his agreement.

Alberto Tibaldi

## Chapter 1

## Architectures of radio systems

The goal of this lecture is expose an overview of a radio system, studying the general architecture in order to identify the function that a radio system must have to work correctly.

The architectures that we will discuss in this text are *heterodyne*: with this word we identify a basic architecture based on a technique that can be used with analog or digital technologies; usually, in an electronic system, there are both analog and digital blocks, but digital parts are the most important: easy to design and realize.

We will use, for this chapter (and generally in all the text) a *top-down approach*; it means studying the functions that the system blocks must realize, then how to realize it with electronic circuits. Which is the top in a radio system? The answer is easy: what is required for the user! With a radio system we must listen to music, speak, or something else. The first thing to do now is define the application and then identify an interesting block to study.

## 1.1 Receiver

A receiver is a radio system block that can select a channel (a range of frequencies) from the source (the air) and reduce the spectral components of all the other channels, so translate the chosen channel in something usable by human (like sounds!).

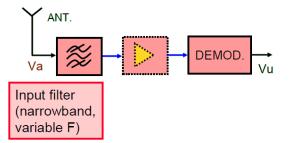

A simple architecture for a receiver can be the following one:

The main blocks are: antenna, narrow-band band-pass filter (that selects the good channel), and demodulator, in order to translate (demodulate) the signal (from AM, FM...).

This architecture works: shifting the response of the band-pass filter we can choose different channels, different signals; using as band-pass filter a resonant circuit.

Changing the reactive parameters of this circuit we can choose one or another signal. Problem: a resonant circuit like this is difficult to use: it can not remove all the other channels, because designing a filter with shifting frequency and narrow band is very very hard. The problem is so the impossibility to obtain a good channel isolation, so to choose only a signal and have possibility of change the channel.

### **1.1.1** Heterodyne architecture

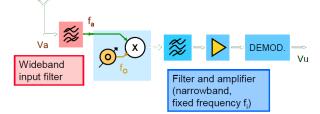

The basic idea that can resolve our isolation problem is the use of an architecture like this:

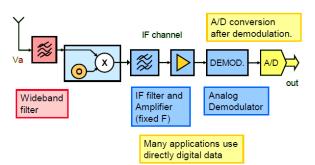

This architecture has the antenna, followed by a wideband filter (useful to reject noise); there is a new block, then an amplifier-filter and demodulator.

The new block introduce a new way to work: there is a local oscillator that multiplies the signal filtered by the first wideband filter.

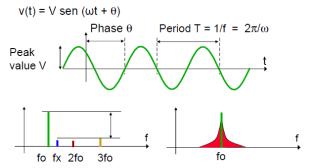

Before the explanations, some remarks: every signal can be identified in the following way: a  $x_t(t)$  signal is equal to a x(t) signal multiplied by a sine/cosine, that take account of its translation on the spectral domain:

$$x_t(t) = x(t) \cdot \cos(2\pi f t)$$

Where f is the middle of the spectrum of the signal. Let's now remark the well-known Werner's formulae:

$$\sin f_1 \cos f_2 = \frac{1}{2} [\sin(f_1 + f_2) + \sin(f_1 - f_2)]$$

$$\cos f_1 \cos f_2 = \frac{1}{2} [\cos(f_1 + f_2) + \cos(f_1 - f_2)]$$

$$\sin f_1 \sin f_2 = \frac{1}{2} [\cos(f_1 - f_2) - \cos(f_1 + f_2)]$$

This formulas are very useful in order to understand what happens when two sine waves are multiplied: the output of the multiplier is composed of two terms: one with frequency  $(f_1 + f_2)$ , the other with frequency  $(f_1 - f_2)$ . All this terms are multiplied for x(t), the signal in base-band (centred on 0 Hz).

If there is a x(t) signal, by multiplication we can translate its spectrum: ignoring (in all of this text) the  $(f_1 + f_2)$  term, the final frequency of the signal it's  $(f_1 - f_2)$ ; tuning the local oscillator to a frequency in order to be, respect to the  $f_{rf}$  term (the frequency of the signal out of the antenna filter), in a  $f_{IF}$  frequency for what:

$$f_{LO} - f_{rf} = f_{IF}$$

The multiplication will generate a signal translated in  $f_{IF}$ .  $f_{IF}$  is the Intermediate Frequency: that is a **fixed** frequency set by the designer, where the multiplication block must shift the former signal, naturally only after have well set the  $f_{LO}$ , the frequency of the Local Oscillator. The variable parameter is not the final frequency or the frequency of the channel, but only the frequency of the local oscillator, before the multiplication realized by the mixer. The multiplication do the separation, so, in  $f_{IF}$  we can design a band-pass filter easily and with better parameters: design a filter in a fixed frequency is better than in variable frequencies, because by this way we can obtain good parameters (like the quality factor, Q, quantifying the selectivity of the filter: with high Q, band is narrower).

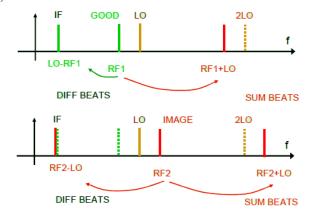

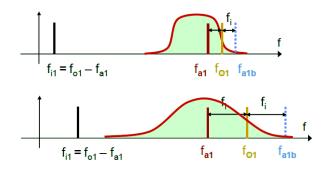

Problem: this technology is based on a system that can shift signal spectrum if it is far from the oscillator frequency exactly  $f_{RF} - f_{LO}$ . There is another critical frequency: a frequency for whom  $f_{IF} = f_{LO} - f_{RF,2}$ : in this case, if there is some spectral content on this frequency (the symmetric frequency respect of the  $f_{LO}$ , the frequencies shifted are two: the good one  $(f_{RF})$  and the bad one  $(f_{RF,2})$ : the second one is usually called *image*: if the local oscillator is exactly between two signals with the same frequency difference respect to the  $f_{LO}$ , the mixer will take two signals instead of one.

How can we handle this? There are many ideas in order to do this:

- The first idea can be the following one: use a radiofrequency filter (the one which follows the antenna output) with narrow band we can erase part of the image frequency; there are two sub-possibilities at this point:

- If we use a big  $f_{IF}$ , so consider large frequency differences, we can use the effects of the radiofrequency filter and have reduced spectral components for the signal far away from the good one (including in this components the image frequency one!);

- The previous sub-point is interesting but also has a problem: high values of  $f_{IF}$  cause problems in designing of the IF filter: design a narrow-band filter (with good parameters) in high frequencies is very difficult, so we remove images, but we can't obtain an excellent selection of the channel.

This problem appears also in the first part of this idea: this idea is based on introducing a narrow band (not very narrow) in radiofrequency spectrum, and this is very very difficult (and so expensive) to have. This idea is realizable, but not very good. The parameter that quantifies the qualities of a filter is the factor quality parameter, Q: it is very difficult to have high Q (and so narrow band) in high frequencies. A last note: for the radiofrequency, with this idea, the equivalent system is like having a moving filter (IF filter); from the point of view of the filter, it's like to have a shifting spectrum; what really happens is different from both the points of view: the local oscillator with its frequency it's multiplied for the signal, and due to the Werner's formulae we know that there is a shift of the signal.

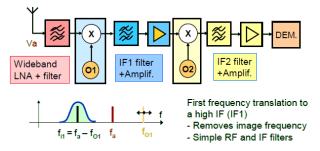

• Filtering and design filter is hard, expensive, so often it's not the good way to take: from one side we want high IF frequency, from the other side a low IF (in order to increase Q). Can we get something that makes everybody happy? The answer is yes: do the frequency translation twice: dual converse.

The first IF is in a high frequency, the second one in a lower frequency respect of the first one, in order to have a narrow band filter easy to design and removing (with the first IF) image effects. There is, after the first translation, another possibility for images; the filter in the middle of the two mixers is useful for this reason: remove components or images before the second translation. There are systems with three of four conversions; the problems are for the filters, cause give a good shape to the filter can be hard, so expensive.

In order to realize filters, there are different ways:

- LC circuits, so electronic resonators (already seen);

- Mechanical filters: electronic circuits with mechanical elements that can have filtering effects, like LC resonators.

### Mechanical filters

Some years ago in high quality audio system the best way in order to realize filtering effects was the use of SAW, so of mechanical filters; SAW (surface acoustic wave) filters are electromechanical devices commonly used in radiofrequency applications. Electrical signals are converted to a mechanical wave in a device constructed of a piezoelectric crystal or ceramic; this wave is delayed as it propagates across the device, before being converted back to an electrical signal by further electrodes. The delayed outputs are recombined to produce a direct analog implementation of a finite impulse response filter. This hybrid filtering technique is also found in an analog sampled filter. SAW filters are limited to frequencies up to 3 GHz.

With quartz filters there are small metallic boxes that contain quartz oscillators: they are the base block for almost every good oscillator/tuned circuit. This can be used in order to realize also narrowband filters.

SAWs use ceramic materials, and are less expensive of the quartz lattice filters, but can produce something similar. The RF filters for the cellular phone use this technology.

### 1.1.2 Complex filters: SSB

There is another way to relax the specifications of filters, using the theory hidden in the Werner's formulae; as we already remarked before:

$$\sin f_1 \cos f_2 = \frac{1}{2} [\sin(f_1 + f_2) + \sin(f_1 - f_2)]$$

$$\cos f_1 \cos f_2 = \frac{1}{2} [\cos(f_1 + f_2) + \cos(f_1 - f_2)]$$

$$\sin f_1 \sin f_2 = \frac{1}{2} [\cos(f_1 - f_2) - \cos(f_1 + f_2)]$$

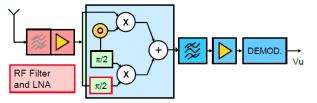

Now: we know that sine is a cosine shifted by  $\frac{\pi}{2}$ ; what we can do now is use this relations and delete with the maths the bad signal: the image

frequency! If we have on one side the multiplication of two cosines, on the other side the multiplication of two sines, adding the results we obtain:

$\cos f_1 \cos f_2 + \sin f_1 \sin f_2 = \cos(f_1 - f_2)$

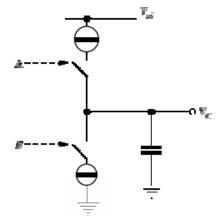

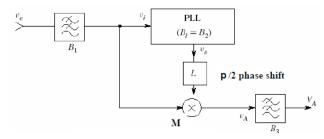

An architecture that can realize this idea is the same:

With the phase shift device we can change the cosine wave in a sine wave with the same polarity, so remove with the adder the image frequency without using filters. In order to have many channels in the spectrum, we can use SSB modulation (Single Side-Band): with a phase shifter and this technique we can obtain the SSB.

This architecture solves every problem? The answer is yes, but we have yet some problems: this architecture is used in commercial devices only since four-five years, because it requires very tight matching of gain and phase rotation of the signal; if this condition is not satisfied, positive and negative components don't delete by themselves and the system does not work. This can be done now with integrated circuits: although this technique exists since the World War II, it was for many years very expensive to realize, so useless.

Let's analyse better this architecture: there are two groups of phase shifters: the left ones and the right ones. The left ones are critical: they must change in a wide band but with a great precision; with their, our local oscillator can generate both sine and cosine waves, over a wide range of frequencies; the other left-side phase shifter is connected to the output of the antenna, so it must work in a wide frequency range. The right one is on the difference, on the IF: at IF, so in a fixed frequency, the previous problem does not exists, so we must build a phase shifter that works on a single frequency, in a very narrow band (the filtered one), and this is easy.

Another block present in the architecture is the LNA (Low Noise Amplifier): out of the antenna there is a microvolt (or less) voltage, so noise has a little amplitude; due to this reason, we write about low noise.

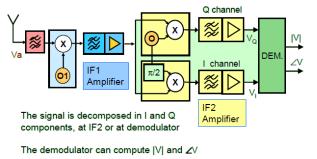

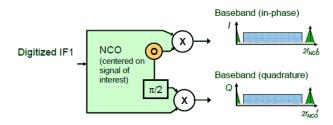

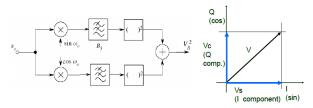

### I/Q demodulation

We have, after the previous subsection, sine and cosine (thanks to the phase shifter); an idea to realize a radio system architecture is use a phase/quadrature

modulation, so decouple the signal in two components, multiplying it to sine and cosine:

### Zero-IF receiver

The idea of heterodyne architecture was shifting the signal spectrum to a frequency range lower than the former one; the idea of zero-IF receivers is moving the spectrum in base-band, using as center of the bandwidth the DC frequency: 0 Hz. The main difference is that we don't need a band-pass filter after this shifting, because it's enough the use of a simple low-pass frequency response; the low-pass filter can be realized easily respect to the band-pass one, and we can use op-amps.

There is also a problem: in zero-IF transmitter, DC becomes the signal, so there are problems with op-amps and other electronics because of the hardware offsets. There is another problem: if there is a noise at the same frequency of the signal, isolation for the local oscillator is impossible.

Another problem: the image frequency can exists, if there is a signal in the other side of the spectrum respect of the 0 Hz: shifting from  $f_{RF}$  to 0 Hz the signal, we will shift also the  $-f_{RF}$  one, obtaining an overlap of the spectrum. For this reason, zero-IF cannot be realized with only one mixer; however, this is a good technique, because of the filter required: low-pass are very easy and cheap!

The presence of low-pass filters is a characteristic for this architecture: if in a schematic we see a low-pass filter, we can be sure that this is a zero-IF architecture, because it is the only one that can use this kind of filters.

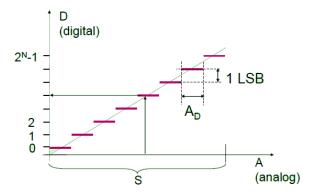

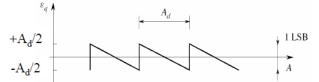

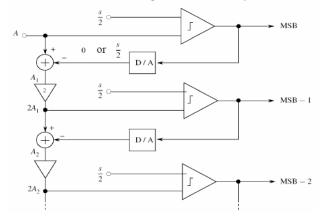

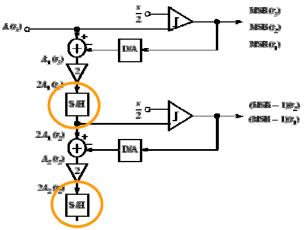

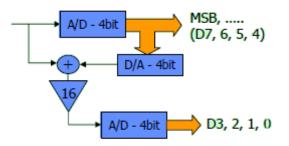

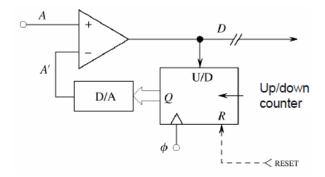

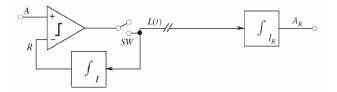

### **1.2** Digital receivers

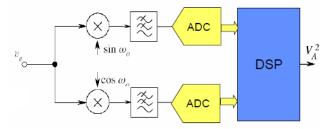

Until now we have studied the heterodyne structure for receivers and transmitters; we have learned what are the image frequencies and how to remove they by filters or some other ways; all the system studied have a common characteristic: they are all analog, so based on analog electronics. In this years electronics focused their studies and researches on digital realizations: they are cheaper, useful for new media like satellites, and more insensitive respect to noise: due to the fact that there are only two possible levels, noise cannot disturb in a great measure the information and elaboration of the circuits; another reason: with digital electronics is possible to handle hard modulations or other function in an easy way, just by programming a DSP, a processor.

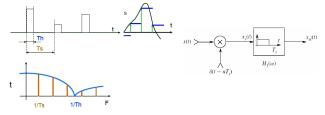

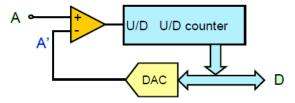

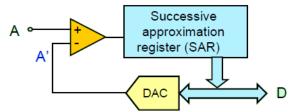

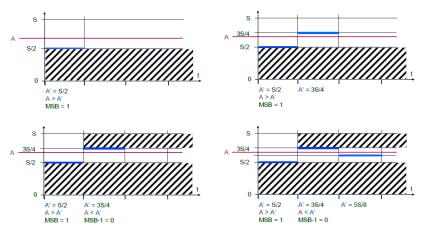

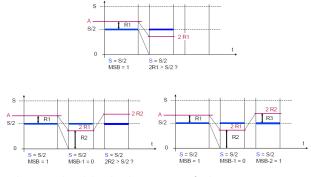

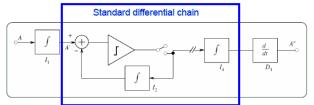

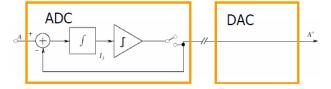

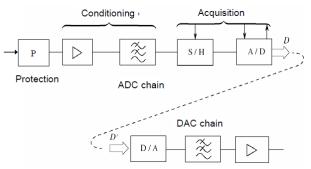

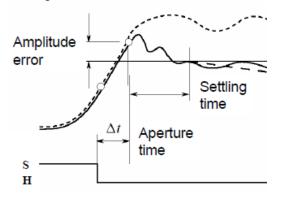

This section will explain how to realize a digital receiver in many ways, describing the differences between the various architectures. The block that realizes the transformation from the analog world to the digital world is the A/D converter (Analog to Digital converter): from the place in the block diagram where the A/D is inserted to the end of the block diagram, all the blocks will become digital.

There are many ways to use an A/D converter; let's study all of them:

• First way: put the A/D converter out of the demodulator:

The demodulated signal will be transformed from analog to digital; on digital we can do easily error correction, encryption or other functions that can be implemented on analog signals, but really hardly.

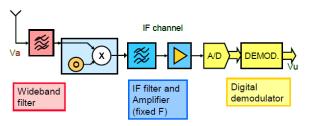

• Second way: A/D converter between output amplifier and demodulator:

The digital demodulator can use complex algorithms The same HW support different types of modulation The A/D converter must operate at high frequency

With this architecture we can demodulate the signal with digital systems, so programming the processor! If IF is centred in a low frequency, the sampler can be simple to realize technologically; this is the first step in order to realize a software radio.

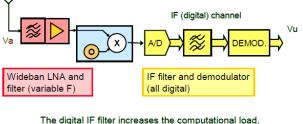

• Third way: put the A/D converter after the mixer:

but allows to modify the IF parameters in the SW

Well, the IF frequency is the same, but now the DSP must realize also digital filtering functions; design a digital filter is more easy that an analog filter: we must only program a processor instead of change values for capacitors or inductors. There is a drawback: we need a processor which requires more power respect to the previous situation: for filtering function we require more computation power, so much more energy to provide to the system.

In order to have a good converter it must represent all the values out of the antenna; in order to do this, there are two ways to design the system: design an A/D converter with many bits, in order to represent correctly also the small values, or use a VGA (Variable Gain Amplifier): if the amplifier amplifies only the small parts of the signal out of the antenna filter, we can describe the smaller signals as the bigger one, with the same precision and without using any more bit.

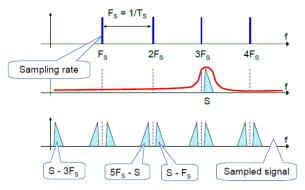

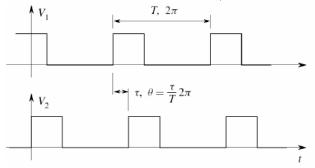

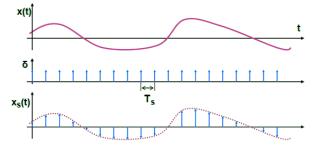

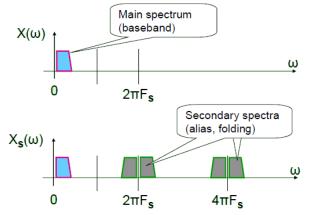

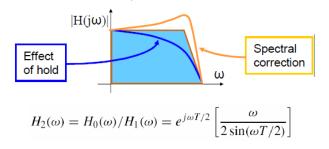

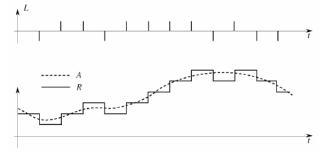

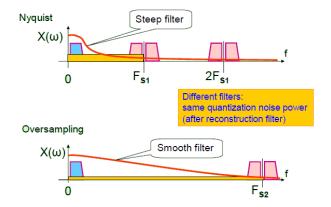

### **Remarks about sampling**

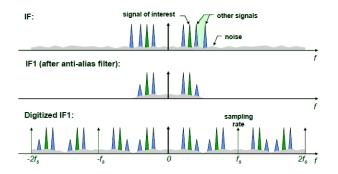

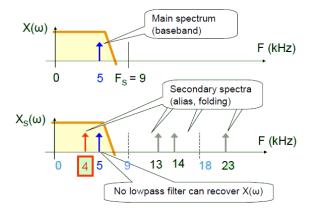

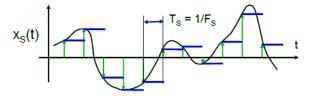

Let's remark now what happens when we sample a signal: every time we sample a signal, in the time domain we multiply the signal with a train of pulses; as known from the Signal Processing course, a train of pulses in the time domain has, as spectrum, a train of pulses. We have something like this:

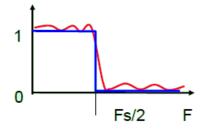

This picture can show the meaning of the Nyquist criteria: sampling generate replicas of the spectrum of the original signal, centred in the double of the base frequency, the triple, and so go on (back and forward); if we sample with a frequency smaller than  $2f_B$ , where  $f_B$  is the bandwidth of the signal we consider, we have aliasing, overlapping of the replicas of the spectrum. For this reason, before of the sampling process, we must use an anti-aliasing filter, realized by a low-pass filter, that erases all the spectral contributes after  $f_B$ , reducing aliasing effects.

### 1.2.1 Digital architectures

Basing on this ideas, there are some architectures:

• Second conversion (with phase and quadrature): using two conversions, the digital signal we have can be treated as an image; the digital processor can be used in order to edit or elaborate digital images, using as components the phase and quadrature ones.

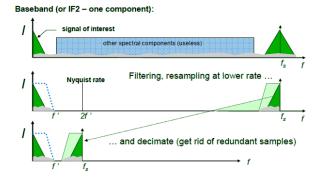

• Decimation: we can reduce sample rate in order to use less power:

If there is a spectral range not interesting for the elaboration, with a filtering process we can reduce the sample rate and obtain a better signal to handle.

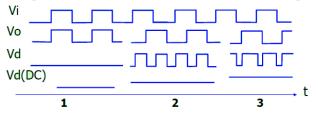

### Samplers as mixers

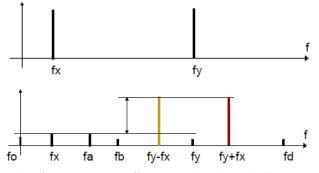

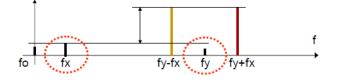

The most interesting application merit a dedicated subsection. An introduction: as known, the frequency shifting is realized by multiplying a cosine wave (or sine wave) to a signal, in order to obtain a signal centred in the difference of the two frequencies; we also remarked that a train of pulses in the time domain has as spectrum a train of pulses in the frequency domain; every pulse (Dirac delta signal) is a sine wave, as known from the theory of Signal Processing; we can say that a mixer can be replaced by a sampler, considering a good frequency: depending on the frequency of the spectrum of the delta train, we have different contributes; let's consider this example:

If the only spectral range interesting for the radio elaboration is the one near to  $3F_S$ , where  $F_S$  is defined as:

$$F_S \triangleq \frac{1}{T_S}$$

And  $T_S$  is the sample time.

The sampling process is so used also as frequency conversion process: changing the sample rate we can change  $F_S$ , so change channel and part of translated spectrum.

Obviously, we have a problem: this A/D conversion is not simple to design, because it works in radiofrequency; the only device before it is the anti-alias filter, that removes RF noise (LNA).

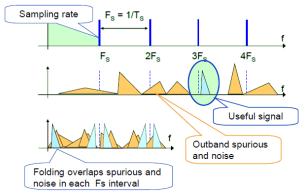

Sampling (or oversampling) with respect of Nyquist criteria, we can rebuild the signal. Previously we looked a particular case: the one with the useful signal in the middle of the bandwidth. As we seen, by multiplying for the 3rd delta signal we obtain  $S - 3F_S$ , so we same thing. A note: we don't sample at Nyquist frequency, because we don't consider the other spectral contents (before and after the useful signal). This case can be very useful if all the channels are in the center of the total bandwidth. By violating Nyquist, we obtain a confused signal, that cannot be treated with any kind of technology:

Here we have the filtering effect: by filtering, so isolating the set of the channels (the useful range of the frequencies) we subsample: we violate the Nyquist criteria, but we don't have problems, because of the elimination of all other elements; the final result is similar to the IF translation; after the translation, we can use a lowpass filter in order to rebuild the signal.

The important thing is the signal bandwidth, so the wideness of the channel bandwidth, **not** the carrier frequency: sampling can move the spectrum back as the mixer + oscillator, by subsampling. Let's understand one thing: the Nyquist criteria must be respected, but only in order to avoid aliasing problems in the final result: we subsample respect to the carrier frequency, not respect to the wideness of the set of channels: if the set of channels has a bandwidth large 300 MHz, we **must** sample at least at 600 MHz, the double of the wideness of the bandwidth. The individual channel so can be isolated with digital sampling, with techniques based on processor programming, using analog electronics only for the radiofrequency filter (the one that deletes all the non-interesting parts of the spectrum).

The main idea for a radio system must be this: go to digital as soon as possible: to digital, all become easier. The best idea is undersampling (subsampling); with two images, as already wrote, we can do image cancellation with no filtering.

In modern devices or products, the radiofrequency filter it's large enough to keep all the channels; professional receivers have more filters, so depending on the situation they choose one or another; tri-band cellular phones are an example of this thing: three band that they can use, so three radiofrequency filters!

We wrote so much about receivers, but nothing about transmitters; this is not necessary, because the architectures of the transmitters are equal to the ones for the receivers, less then amplifiers: in receivers we use LNA, Low Noise Amplifiers; in transmitters PA, Power Amplifiers, that have, often, non-linearity problems.

## Chapter 2

# Linear and non-linear use of bipolar junction transistors

In radio systems an engineer must use very often amplifiers: amplifiers are necessary every time we need to change the amplitude of a signal, increase its power or something similar. There are some ways to design amplifiers: with operational amplifiers, with transistors or with other devices. Operational amplifiers are very easy to use for designing, but they have a big problem: the bandwidth that they can provide is small; over some megahertz an op-amp can not work. Because of this, transistor amplifiers are the best way to design and realize an amplifier for radio systems: transistors can work with signals up to 10 gigahertz frequency, if the designer is skilled (but this boundary is shifting!). Transistor amplifiers are really useful in radiofrequency: near antennas or other radiofrequency/microwave devices, op-amp are totally useless, and the best solution is use transistors.

In this chapter we will study first linear models (small signal models) of the bipolar junction transistor, focusing in analysis and then in design (studying ways to choose amplifier gain, output voltage swing, amplifier bandwidth), so we will use non-linear models, in order to study other applications of the bipolar transistor, based on the Ebers-Moll model (and its exponential relation between voltage and current).

The general symbol of an amplifier is this:

In theory if we put in an amplifier a signal  $v_i$  we must have an output  $v_o$  like this:

$v_o = A \cdot v_i$

$v_i$  and  $v_o$  must have the same shape, only re-scaled by a factor A. There are some non-idealities:

• In every electronic system there is **noise**: every block adds additive noise, n(t):

$$v_0 = v_i \cdot A + n(t)$$

• The shape of the signal can change:

the amplifier can have saturation effects or something similar: slew rate, phase distorsion or something else. In order to consider this effect, can be useful consider the Fourier series of the distorsion<sup>1</sup> of the signal:

$$v_0 = v_i \cdot A + n(t) + (v_e^2, v_e^3 \dots v_e^n)$$

$v_e$  is the error signal in the system.

For amplifiers we need to have only the re-scaled term: we want to keep only this function:

$$v_o = A \cdot v_i$$

To obtain this, we will study ways to have better linearity; another part of this chapter will study applications of non-linearity, but later.

Now, we will have some remarks for some "famous" circuits, and learn to design on they.

There are many types of transistors: BJT (bipolar junction transistors), MOS, FETs or other; on the small signal model, BJT or MOS are equal; while we move on large signal, there are some differences: for BJT there is the Ebers-Moll model, the well-known exponential relation, easy to analyze and use. For MOS transistors this is not true: there are many equations that describe the behaviour of the MOS in different work regions, or "operating points"; there are different models for every device and for every operating point we want to use. In this text we will study the maths for only BJT, because it's easier: BJT can be handled with maths, MOS only with simulators. There are tricks for control non-linearity and distorsion; we will study this tricks on BJT, but don't worry: they can be applied without problems also in MOS transistors!

<sup>&</sup>lt;sup>1</sup>A little note: there are some functions, some devices, that need distorsion; mixers are an exemple of this functions.

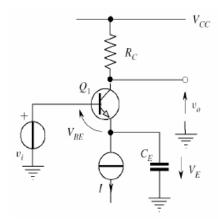

## 2.1 Topology and biasing selection

There are three topologies to realize single stage amplifiers; for *single stage amplifiers* we mean amplifiers realized with a single transistor; every stage takes its name from the name of the pin connected to ground (to the "common" pin). This three topologies are *common emitter*, *common collector* (or *emitter follower*), *common base*.

• The common emitter topology is the most important topology of the three: with CE we can amplify both voltage and current (especially voltage).

• The common collector topology is useful in order to realize a voltage buffer: the voltage gain is almost one, but the current gain is higher; this circuit has large input impedance and small output impedance, so it can be used to improve the CE topology, realizing a better voltage amplifier.

• The common base topology can be used in order to amplify very high frequency signals or to realize particular stages.

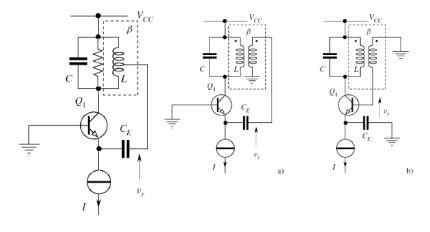

### 2.1.1 Biasing of the common emitter topology

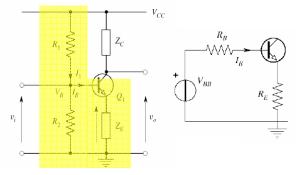

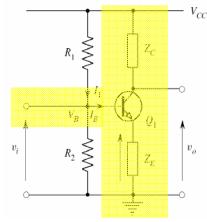

The best topology to realize single stage voltage amplifier is the first one: common emitter topology. For every amplifier, the designer must choose some parameters; the first parameter is the operating point, or **bias point**. The question is: how can we set the operating point of the amplifier? The answer is quite easy; look at this picture:

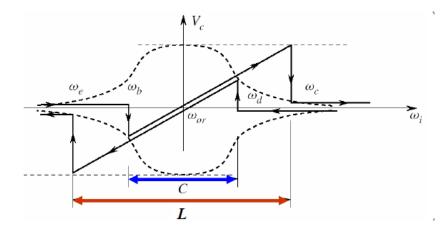

The curves represent the different working point that the device (BJT) can use; there is a line, representing the values of voltage and current that can be assumed by a linear net (a circuit composed by resistors, capacitors and inductors: linear devices). Choosing the net we can choose the bias point of the amplifier in order to satisfy specs.

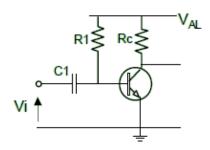

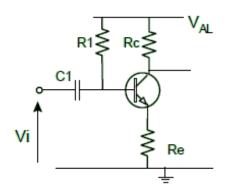

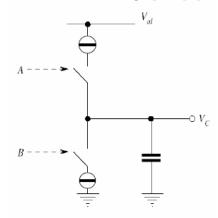

The first step is choose a supply voltage for the circuit; it can be named  $V_{al}$  or  $V_{CC}$  (the second one is interesting: the capital V means "DC voltage", and the CC means supply voltage on collector side). Connecting resistors (in order to have a small current) between the device and the voltage source, we can have a first circuit like this:

This is not a good schematic: the collector current is not fixed, because it depends on the  $\beta$  parameter (current gain); we have something like this:

$$I_B = \frac{V_{CC} - V_{BE}}{R_B}$$

But

$$I_C = \beta I_B$$

Can we decide the operating point now? No! We don't know the exact value of the current gain  $\beta$ , cause we have a bad tolerance on this parameter.

Second step is introducing a resistor on the emitter,  $R_E$ :  $R_E$  works like a negative feedback, because if the current on it increases, increases the voltage on it; on the other side, if the voltage in the emitter increases, the other voltage values decreases (the  $V_{BE}$  voltage, that controls the operating point of the device), so the current gets stable.

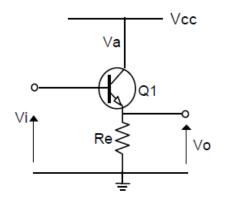

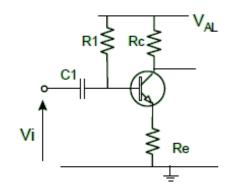

We want a good collector current; with this schematic there is still dependance by  $\beta$ ; an idea can be the use of the famous *self-biasing circuit*:

Choosing the good parameters for this circuit, it can be proof that the voltage gain is like:

$$A_v \simeq \frac{R_C}{R_E}$$

If we use this schematic we have one more problem: if we want to choose the gain of this stage, we must change the bias poin; that's no good at all. How can we change this? Well, we don't matter if the operating point and the model of the circuit for small signals are different: we only need to realyze amplifiers! What we can do is use circuital (possibly linear) elements that can decouple some resistors from the other component of the circuit, in order to have a behaviour for the DC different to the behaviour for the small signals. The solution can be this:

Does this capacitor modifies the operating point? No! OP depends only on DC, but, after a transient, so in the steady state, the capacitor becomes full of charge, and it can be modelized by an open circuit. If the capacitor is big enough, it introduces a pole in the frequencies near the zero hertz limit, so it won't change the behaviour of the circuit in the good frequency range (where it must work as amplifier): it will be modelized with a short circuit, for frequencies higher than the pole's one.

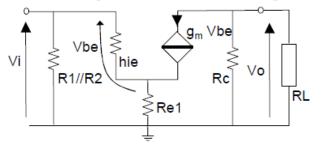

Here is the equivalent circuit of the amplifier (in linearity):

Remember that now we are only interested about changes of voltage and current (signals): since we are analyzing changes, the DCs are not important. On the emitter there is, as resistance,  $R_1//R_2$ ; on the collector there is only  $R_C$ . The voltage gain can be calculated as:

$$A_v = \frac{v_o}{v_i}$$

Where

$$v_o = -g_m \cdot v_{BE} \cdot R_C$$

Because, as we can see in the equivalent model of the amplifier,  $V_{BE} = v_i$ . So:

$$A_v = -g_m \cdot R_C$$

This is the gain in this circuit, and this is not so good: gain depends on  $g_m$ , that depends on the operating point chosen for the circuit.

In order to end this section, a little remark: in DC, the capacitor is full of charge, so it's impedance is higher than all other impedances in the circuit, and it's modelizable as an open circuit; if the frequency of the signal is high, capacitors have an impedance smaller than the others in the circuit, so are modelizable as short circuits. This can be useful for selecting the gain without touching the bias point: due to linearity, we can decouple DCs and signals and their effects on the circuit, so, using capacitors, we can "show" to different signals different circuits, obtaining a frequency-dependent voltage gain.

## 2.2 Analysis of the circuit

At first, we want to analyze the circuit, in order to get formulas useful to design with it. We are interested only on the resistive part of the impedances  $Z_E$  and  $Z_C$ , so we will consider only  $R_E$  and  $R_C$ .  $h_{ie}$  and  $h_{fe}$  are some of the small signal parameters we are interested to study; in order to not use the circuit in a non-linear zone, we want  $V_{CE} > 0, 2$  volt: if we have a smaller collector to emitter voltage, the transistor works as a switch, not as an amplifier, and distorsion effects change the shape of the signal.

### 2.2.1 Analysis of the bias point

Beginning with the already shown circuit, we can use the Thvenin equivalent circuit, obtaining:

Where:

$$V_{BB} = V_{CC} \cdot \frac{R_2}{R_1 + R_2}$$

$$R_B = R_1 / / R_2$$

Now, let's write an equation for the mesh of the circuit that don't go through the collector, obtaining:

$$V_{BB} = R_1 / / R_2 \cdot \frac{I_E}{\beta + 1} + V_{BE} + R_E I_E$$

If the circuit is well designed, the first term (depending by  $\beta$ ) will be near to 0; as known, a typical value for  $V_{BE}$  is 0,6 volt.  $I_E$  can be evaluated with this:

$$V_{BB} \simeq 0, 6V + R_E I_E$$

With this and the other mesh we can evaluated the  $V_{CE}$  voltage:

$$V_{CE} = V_{CC} - R_C I_C - R_E I_E$$

If  $V_{CE} > 0, 2$  volt, we know that the circuit works in a good zone, so that we are far from the saturation area.

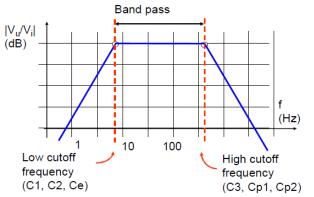

### 2.2.2 Bandwidth

In this text there was nothing written about amplifier bandwidth. A good designer must limit bandwidth for a reason: many bandwidth, many noise: the stochastic process more often used in order to modelize noise in electronic systems is the white gaussian noise, that exists in every zone of the spectrum; limiting bandwidth we can limit the incoming noise, increasing the performances of our system.

How can we control bandwidth? Somewhere this question was already answered: with capacitors! Capacitors (like inductors, elements no more used because very difficult to integrate) can show, as previously written, show to the signal different circuits depending on the its frequency, hiding or showing other elements like resistors or something else. Where must we put capacitors? Well, there are substantially two ways to use capacitors:

- Putting they on series to other elements: putting a capacitor in series introduces a transmission zero for this component, so a high-pass response; this can determine the low frequency response of the circuit or of a part of it;

- Putting capacitors on parallel (connected to ground) have a dual effect: the capacitor for low frequency is hidden by his big impedance, but for high frequencies he becomes a short circuit, so connect a pin to ground, and stop the signals on its way. This is a low-pass response: this way to use capacitors permit to determine and set the high frequency response of the circuit.

Sometimes we can see capacitances between base and collector of the transistor; they are not capacitors, but parassite capacitances; for now, we don't consider this on circuit.

## 2.3 A design example

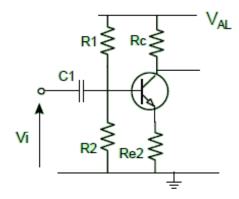

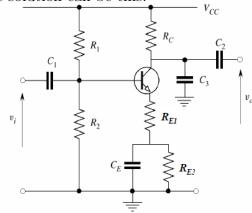

Design an amplifier with the following specifics and schematic:

- Voltage gain  $A_v = 15$  (nominal);

- - 3 dB bandwidth from 200 Hz to 20 kHz (minimum);

- output dynamic at least 4 Vpp on 10 kiloohm load (or higher);

- supply voltage 15 V (nominal);

- 2n2222A Transistor.

### 2.3.1 Resolution

### Bias point

The operating point of the amplifier must be chosen in order to choose the output swing. There are many ways to start design, here is proposed one of these. We want at least 4 volt peak-to-peak of output voltage swing with a load of 10 kiloohm. This indication is useless: bias point must be decided without introducing load in the circuit (in the beginning).

For the signal, the equivalent circuit is this:

When we connect the load to the circuit, we have a voltage divider. The idea can be the next (it's NOT the only way to follow!):  $V_u$  must be obviously higher than 4 volt, so let's suppose 8 volt, in order to have  $R_L = R_C$ : the divider becomes equal, and on the load we obtain half of 8 volt, so the 4 volt of the specs.

Now: with 8 volt of swing on the collector, remembering that the highest voltage on the collector can be 15 volt (the supply voltage); the minimum voltage on the collector is the difference of 15 and 8: 7 volt! Due to avoid saturation, we must impose a voltage between collector and emitter of almost 0,2 volt; we choose 1 volt in order to keep us far away from the saturation zone. Imposing 6 volt on the emitter we can guarantee that the threshold will be respected. What is the value of the current  $I_C$ ?

$$I_C = \frac{15 - 11}{10 \cdot 10^3} = 0,4\text{mA}$$

### Voltage divider

What do we need now? Well, we now can calculate the ratio of the voltage divider on the base: we have the voltage on the emitter and the  $V_{BE}$  voltage drop, so:

$$V_B = 6 + 0, 6 = 6, 6V$$

This is one constraint of the problem; the other constraint is that we need the base current: we have to take account of the value of  $I_B$  in order

to calculated good values for the base resistances. Don't forget one detail: we don't know  $\beta$ , the current gain! Let's use a  $\beta_{min}$ , which can be found on datasheets; with  $\beta_{min} = 50$ :

$$I_{B,MAX} = 8\mu A$$

In order to make the voltage here not related with this current, if we make the current on the  $R_2$  resistor much higher than 8 microampre, we are ok; let's not have a huge current: this can dissipate power on the resistors due to Joule effect. Choosing a current 10 or 50 times greater than the other, we are ok.

### Voltage gain

For the voltage gain, found the bias point, we must study gain and its frequency response. What must we do now? Well, the frequency response of this system is something like this:

In the frequency range where the circuit works as amplifier, we must impose a voltage gain. This can be done easily:

- From the collector, we see a resistance of  $R_C//R_L$ ;

- From the emitter, we see a resistance of  $R_{e1}$ .

So:

$$|A_v| \sim \frac{R_C//R_L}{R_{e1}}$$

Because  $C_4$  is closed,  $C_3$  is open. There is a more precise formula:

$$A_v = \frac{v_o}{v_i} = -\frac{Z_C h_{fe}}{h_{ie} + Z_E (h_{fe} + 1)}$$

For the frequency limits,  $C_3$  and  $C_4$  must be calculated in order to put poles in the position requested by the specifics of the circuit.

## 2.4 Non-linear issues on transistor amplifiers

Until now we have analysed a basic transistor circuit to realize amplifiers, in a condition: the linearity. Having signals that can not go out of the output voltage dynamic; in linearity we use the small signal model:

Out of the linearity voltage amplitude range, the analysis cannot be done with the linear model, but there is another good model to use: the Ebers-Moll model, taking account of non-linear effects:

If we put a sine wave in a system with this model, due to non-linearity out of the system we will not have a sine wave, because non-linearity generates other harmonics contributes:

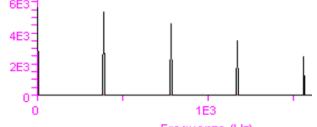

Frequenza (Hz)

Problems of non-linearity in radio systems are in power amplifiers, because signals treated with them is not small; in telecommuncation electronics, non-linearity effects can be good: some functions useful in this context (like mixers) can be realized with there effects.

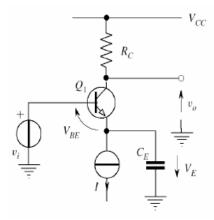

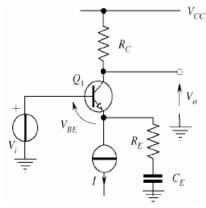

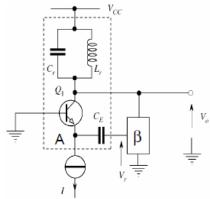

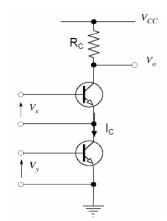

The basic circuit that we will consider is the next one:

Biasing is fixed by fixing the current source on the emitter; supposing that we are interested on signals, variations, we will consider  $C_1$  and  $C_4$  closed,

$C_3$  open; we need something that put to ground the current for the signal but not for the bias, and this is the capacitor; choosing the convention for the voltage sign positive in the lower pin of the capacitor, supposing that the current generator is connected to a voltage reference (not necessary zero, because often we use negative voltages in the emitter). We introduce a sine wave on base (signal with no offset, because it has an average equal to zero), we know that on the emitter there are -0,6 volt (due to the  $v_{BE}$  voltage and because on base there are zero volt of DC). Supposing so that:

$$v_i = V_i \cos(\omega_i t)$$

$$I_C \simeq I_E$$

Then, using the Ebers-Moll equation:

$$I_E = I_S e^{\frac{v_{BE}}{\eta V_T}}$$

Where  $I_S$  is the reverse saturation current, and  $\eta = 1$  in transistors (due to technological reasons). Using down current convention, we can write:

$$v_i = v_{BE} - V_E \Longrightarrow v_{BE} = v_i + V_E$$

$V_E$  is a DC voltage, so it's written with the capital. We can substitute and find:

$$I_C = I_E = I_S e^{\frac{v_i + V_E}{V_T}} = I_S \cdot e^{\frac{V_E}{V_T}} \cdot e^{\frac{V_i}{V_T}\cos(\omega_i t)}$$

Defining the normalized voltage value x as:

$$x \triangleq \frac{V_i}{V_T}$$

We can try to obtain a better equation to study. The critical term is the exponential of cosine; can be proof that:

$$e^{x\cos(\omega t)} = I_0(x) + 2\sum_{n=1}^{\infty} I_n(x)\cos(n\omega_i t)$$

This means that voltage can be decomposed in different contributes depending by harmonics, where every harmonic contribute has a frequency equal to the  $\omega_i$  frequency multiplied by an integer factor n. The coefficients of this series expansion depend on the modified Bessel function of first specie. In order to compute this values, we will use tables. Putting this expression into the old equation, we obtain:

$$i_C \triangleq I_C = I_S e^{\frac{V_E}{V_T}} \left[ I_0(\frac{V_E}{V_T}) + 2\sum_{n=1}^{\infty} I_n(\frac{V_E}{V_T}) \cos(n\omega_i t) \right]$$

The first term (depending by  $I_0(\frac{V_E}{V_T})$ ) is a DC term, so an offset term; with n = 1 we have the fundamental harmonic contribute, so with  $n \ge 2$  the distorted terms, came out due to the non-linearity of the system.

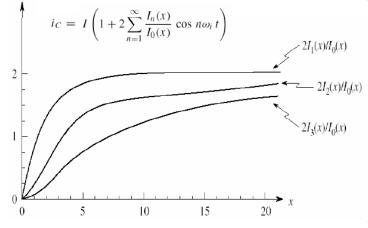

Taking off of the parenthesis the  $I_0$  term, we obtain the following relation:

$$i_C = I_C = I_S I_0(x) e^{\frac{V_E}{V_T}} \left[ 1 + 2\sum_{n=1}^{\infty} I_n(x) \cos(n\omega_i t) \right]$$

So the plot shows the various contributes related to  $\frac{2I_n(x)}{I_0(x)}$ ; a little remark: DC term is *I* times 1; *I* is the DC current. By now we will use the following equation in order to represent the total collector current:

$$i_C = I\left[2\sum_{n=1}^{\infty} I_n(x)\cos(n\omega_i t)\right]$$

$\omega_1$  is the frequency (pulsation) of the fundamental harmonic, and it depends on  $I_1(x)$ ;  $\omega_2 = 2\omega_1$  depends on  $I_2(x)$ , and is the frequency of the second harmonic, the first generated by the non-linearity of the system. With changing of n, the graphs show many contributes for the harmonics.

Let us assume for a moment that we are using a linear model; in small signal model we wrote:

$$i_C = g_m \cdot V_i \cos(\omega_i t)$$

Let's define k as

$$k = g_m \cdot V_i$$

We can write, in the linear model, that  $i_C = k \cos(\omega_i t)$ , where k is the gain of the system; in this case the gain is constant, so the characteristic of the system is a line; this equation represents only the coefficient for n = 1, so the linear coefficient: proportional increase of the amplitude of the output with increasing of the input amplitude.

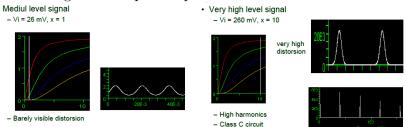

The plot represents the non-linear model of the system; this drawing shows that if we increase the input level output (so increasing x, supposing that  $V_T$  is constant), we obtain for low amplitudes of x a linear response, so a constant gain (we can think that gain is the slope of this curve), and the proportional increase of the amplitude; going to higher level of amplitude of the input signal (so by increasing x), we have no more a linear increase, due to saturation effects of the transistor.

The first part of the model is almost linear: this is the zone where linear model can be used; note that with x = 1,  $V_i = xV_T \sim 26$  mV (about 26 millivolt, but it depends on the temperature); 26 millivolt is a very small signal: if  $V_i = 260$  mV, we are surely in saturation zone! The small signal model works only with small signals, so few millivolt of amplitude! The linear model can't predict the saturation effect because linearity does not generate other harmonics (as known from Signal Processing Theory): a linear model can produce only signals with fundamental component.

Now, considering (as already written) that

$$I \triangleq I_S \mathrm{e}^{\frac{V_E}{V_T}} I_0(x)$$

We can observe something: I is a DC current (so fixed), but it depends on  $V_i$ : if we change  $V_i$  (and so x), we can change  $I_0$  output value;  $V_E$  is a hidden function of x, so I is really fixed, but some particulars were missing. There is a logarithmic dependence between  $V_E$  and x:

$$V_E = V_T \ln\left(\frac{l}{I_S I_0(x)}\right)$$

There is a fact: DC value depends on the amplitude of the input signal: this can happen because we are using a non-linear device, so DC can be modified by signals (this is obviously impossible in linear devices/models!).

We are interested on the output voltage:

$$v_C = R_C i_C$$

If we look only part of spectrum that don't consider DCs we can ignore them; this can be done by studying only the second term of the equation:

$$i_C = I\left[2\sum_{n=1}^{\infty} I_n(x)\cos(n\omega_i t)\right]$$

So we don't consider the 1 in the parenthesis, ignoring DC terms and looking only at variable terms.

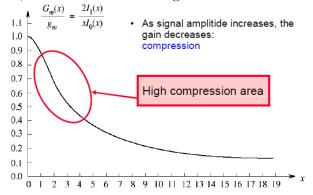

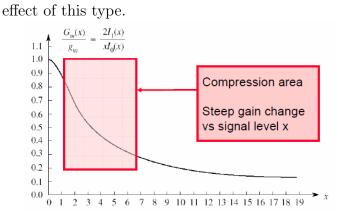

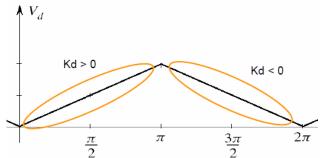

If we look at  $\frac{I_1}{I_0}$  curves, we can see that gain decreases as the input amplitude increases; there is a phenomena called *gain compression*: gain is (as already written) the slope of  $V_o$  on  $V_i$ ; this slope decreases as  $V_i$  increases; if  $V_i$  is high, spurious harmonics have a greater contribute respect to the main one, so gain decreases because the system becomes less linear!

#### Little exercise

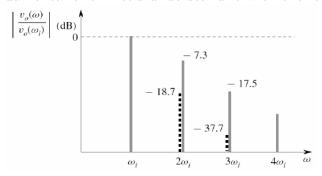

How can we know how many non-linearity is in the system? In other words, how can we quantify the contributes of spurious harmonics respect to the fundamental one? Let's understand it with the following exercise:

Given a transistor amplifier with input  $V_i$ , output  $V_o$ :

$$V_i = 13 \text{mV}; \quad Z_C = R_C$$

The second hypothesis is useful because we don't have to consider the dependence of the output respect to frequency; the question is: draw spectrum of  $V_o$  in dB<sub>c</sub>.

Introduction: decibel (dB) is a measure unit for ratio;  $dB_c$  is a *carrier* dB unit: we calculate the ratio respect to the carrier, so respect to the harmonic with the fundamental frequency.

Our goal is to calculate the second and third harmonics contribute respect to fundamental one; we want:

$$\frac{v_o(\omega_2)}{v_o(\omega_1)}\Big|_{dB} \Longrightarrow \frac{I_2(x)}{I_1(x)}\Big|_{dB}$$

$$\frac{v_o(\omega_3)}{v_o(\omega_1)}\Big|_{dB} \Longrightarrow \frac{I_3(x)}{I_1(x)}\Big|_{dB}$$

So:

$$x = \frac{13}{26} = 0,5$$

$I_1(0,5) = 0,4850 \Longrightarrow 20 \log(0,4850) = -6,283 dB$

$I_2(0,5) = 0,06 \Longrightarrow 20 \log(0,06) = -24.44 \text{dB}$

$$I_3(0,5) = 0,005 \Longrightarrow 20 \log(0,005) = -46.02 \text{dB}$$

So:

$$\frac{v_o(\omega_2)}{v_o(\omega_1)}\Big|_{dB} = 20\log(0,06) - 20\log(0,4850) = -18,15 \text{dB}_c$$

$$\frac{v_o(\omega_3)}{v_o(\omega_1)}\Big|_{dB} = 20\log(0,005) - 20\log(0,4850) = -39.74 \text{dB}_c$$

If values are not good, like x = 1, 54, we must do linear interpolation between the two near values (in the Bessel function's table).

There are two ways, two approaches in order to treat non-linearity:

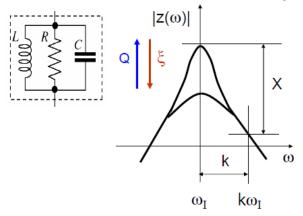

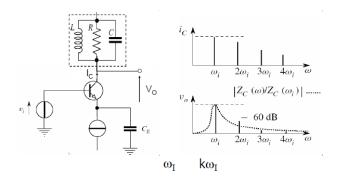

- Fight it: we can remove harmonics using resonant circuits or tuned amplifiers; by removing the harmonics, we have the same gain; of the linear-zone one.

- Use it: we can use harmonics in order to obtain frequency multipliers, VGAs or other particular devices (realizing particular functions).

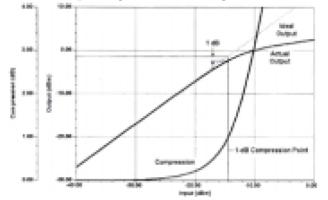

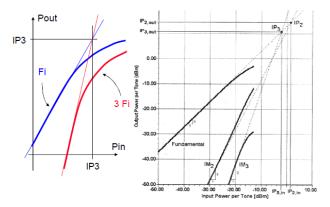

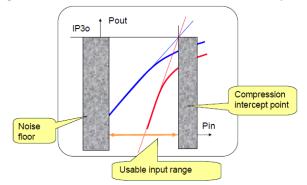

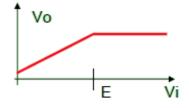

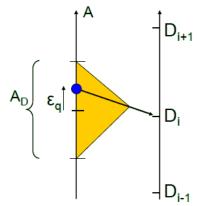

### 2.4.1 Fight non-linearity : Compression

In order to fight non-linearity, we have to know it, so we must introduce some definitions that can be useful to study and avoid problems. The two terms we will introduce are useful because that can be found on datasheets or docs:

- 1 dB compression level

- IP (Intercept Point)

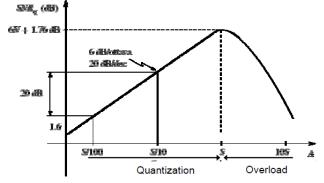

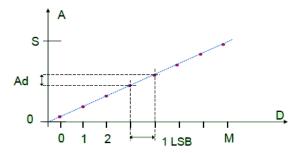

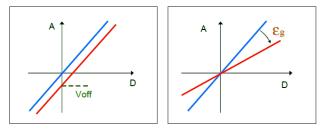

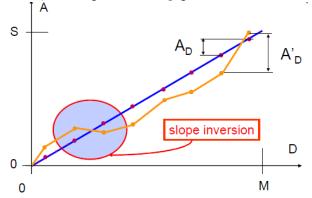

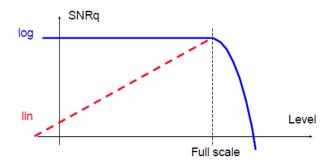

What is 1 dB compression level? Well, as already written, as the amplitude of the input signal increases, gain decreases;

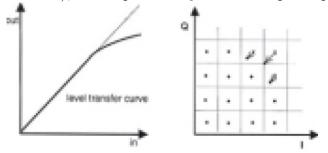

This graph show how the difference of the linear model (small signal model) and non-linear model brings to have a 1 dB difference; 1 dB compression level is the voltage level that gives 1 dB of difference between the ideal output and the non-linear model output. At the begin, compression is zero, because for small signals contributes of 2nd, 3rd and other harmonics is almost zero; by increasing the voltage, that becomes important, so must be quantified (for example with this parameter).

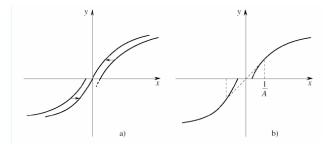

One of the effects of compression related to radio issues can be studied on modulations: QAM is a Quadrature and Angle modulation (digital modulation), that represents symbols on a phase plane:

Compression can be critical because it changes the expected value of the amplitude of the signal, so informations are lost; if the modulation is only

on angle, like PSK (Phase Shift Modulation), compression is no problematic, because all the information is in the angle. The same thing can be written for analog modulations (FM or AM).

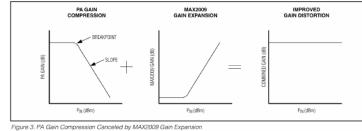

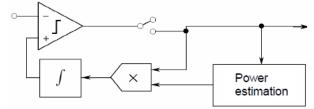

How to correct this kind of problems? Well, an idea can be predistortion: a unit  $P_A$  with distorsion can be compensated by introducing before it another block, with a non-linearity opposite to the one of  $P_A$  (example, put quadratic block before square-root block, logarithmic before exponential, and other...). We can put non-linear corrections in the digital part of the system:

A LUT can implement something like this. The idea is measure the power in the antenna, in order to introduce the non-linear correction, and modify the predistortion information.

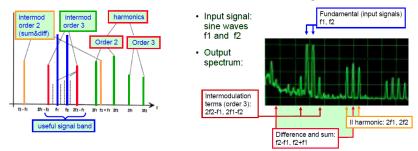

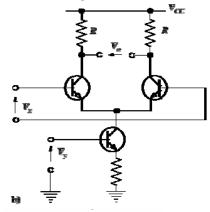

### 2.4.2 Fight non-linearity : Intermodulation

We written about two parameters; one was the 1 dB compression level, already described; now we are going to define another phenomena very bad for circuits, phenomena that can not be fight: intermodulation.

We are reasoning on non-linear circuits, non-linear blocks; there are many ways to express the non linear output; a way can be, given a  $v_i$  input signal, consider the linear term, the quadratic term, the cubic term and so on:

$$v_i \longrightarrow Av_i + Bv_i^2 + Cv_i^3$$

An idea can be use power series expression. If we have a signal with frequency  $f_i$ , the linear term will be the signal with  $f_i$  frequency; the quadratic term will have a contribute with frequency  $2f_i$ , the cubic  $3f_i$  etcetera.

What if our signal is composed by two parts, one with frequency  $f_a$  and one with frequency  $f_b$ ? Well, let's study it:

$$V_i = v_a(f_a) + v_b(f_b)$$

• The linear term will be a linear combination of the two terms:

$$v_{o,1}(f_a) + v_{o,2}(f_b)$$

- The quadratic term, so the second order term, will have signals with frequencies  $2f_a$ ,  $2f_b$ ,  $f_a f_b$ ,  $f_a + f_b$ .

- The cubic term, so the third order term, will be obtained by developing the power of three.

The problem is, with multi-component signals, that spurious harmonics go not only out of the original spectrum, but also **into** the spectrum, so cannot be filtered (without damaging the useful component of the signal). Inband terms can **not** be filtered, so we cannot get rid of them.

What is IP, and how is it related with intermodulation? Well, let's try to show it: if we have  $v_a$  and  $v_b$  with amplitudes  $V_a$  and  $V_b$ , if we increase their values (they are input signals!) until they have values  $2V_a$  and  $2V_b$ , we will have something like this:

- The first order term output will be multiplied by two, like we can expect;

- The third term, so the cubic term, will be multiplied by 8: eight is the third power of two, so the third term harmonic will increase faster than the fundamental: if we increase input level, we can have problems like this, problems that can not be resolved.

The IP3, Intercept Point related to 3rd harmonic, is the intercept point of the linear prosecution of the small signal model, and of the line that can show how third harmonic increases it's level respect to the other.

Second order terms are not important, but third order terms are very dangerous, critical. IP3 can be used to study the dynamic of an amplifier:

Going too low with amplitudes we confuse them with noise; too high, noise it's generated due to compression and intercept point.

In receivers (or transmitters) which is the effect for this phenomena? Well, in transmitters, we generate interference to other channels! In LNA (receivers) we separate channel with IF, but we have too strong components in a part of the spectrum, so due to very strong transmitters (for example, too near to the receiver) we have problems like this.

# Chapter 3

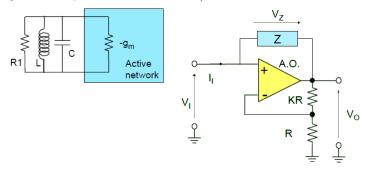

# **Applications of non-linearity**

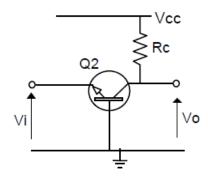

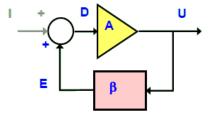

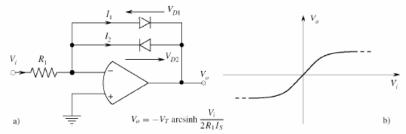

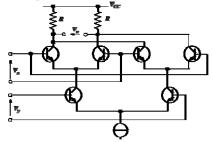

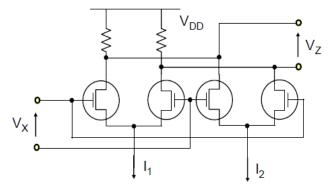

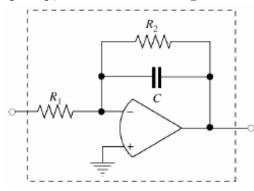

Let's consider the following circuit:

With small signal analysis, we had:

$$v_o = -g_m R_C v_i$$

Now, we want something similar for large signals:

$$v_o(\omega_i) = -G_m(x)R_C v_i$$

This is referred **only** to the carrier  $v_i$ ; this analysis can be used also on tuned amplifiers.

Instead of  $g_m$  we use  $G_m$ : large signal transconductance; it depends on operating point and value of signal amplitude. As known, for the large signal model, the output voltage is:

$$v_o(\omega_i) = -R_C I 2 \frac{I_1(x)}{I_0(x)} \cos(\omega_i t)$$

We want something formally equivalent to  $G_m(x)$ , so we can observe that:

$$v_i = V_i \cos(\omega_i t) = x V_T \cos(\omega_i t)$$

$\implies \cos(\omega_i t) = \frac{V_i}{x V_T}$

So:

$$v_o(\omega_i) = -R_C I 2 \frac{I_1(x)}{I_0(x)} \frac{V_i}{xV_T}$$

Let's observe, now, that:

$$\frac{I}{V_T} = g_m$$

So we found a transconductance; now:

$$v_o(\omega_i) = -g_m R_C 2 \frac{I_1(x)}{I_0(x)} \frac{V_i}{x}$$

$\operatorname{So}$

$$G_m(x) = g_m \cdot 2 \cdot \frac{I_1(x)}{x \cdot I_0(x)}$$

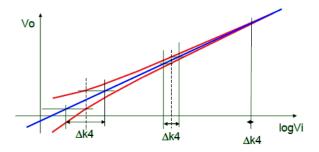

We can calculate and measure the gain for different signal amplitude values, in order to find that gain decreases as amplitude increases:

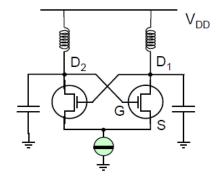

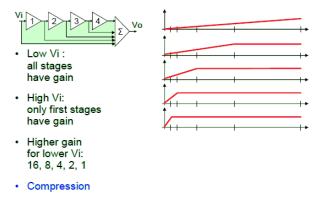

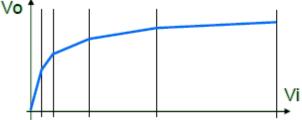

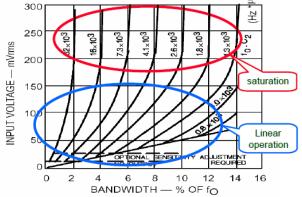

Where to use this? Well, the first idea can be... VGA: Variable Gain Amplifiers! If transconductance changes with signal level, we change gain.

How can we use it? In a FM receiver: we don't want that amplitude change in the receiver, so VGA can be useful! In FM receivers there is a chain of amplifiers that works on this idea. If the receiver is moving, we can obtain some thing with almost the same amplitude. These are compressing amplifiers (for compressing receivers).

And for AM? Compression can be useful because information is in the amplitude; we important part of the amplitude is the relative amplitude respect of different times, but amplitude can change due to movements of the receiver respect of the transmitter (like in cellular phones!). We have something good: signals we consider are in audio band, so 20 kHz; by using high time constant amplifiers, we can measure the power of the signal for a long time, so see changes due to movements and introduce average corrections: changes of averages are very slow respect to the frequency of the signal, so amplifying with high  $\tau$  can be great in order to realize AGC (Automatic Gain Control).

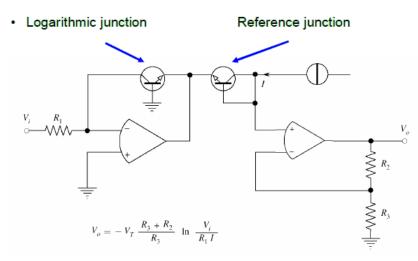

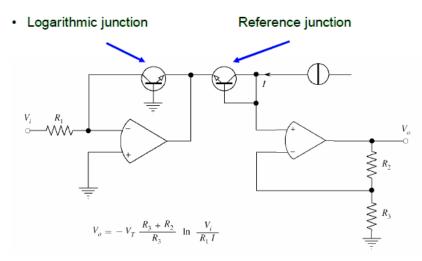

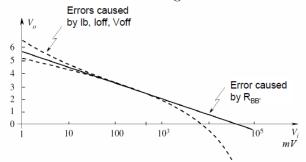

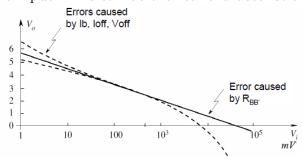

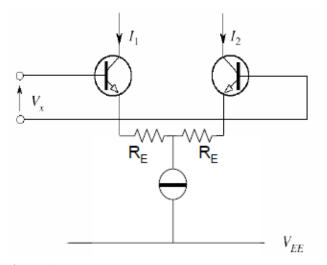

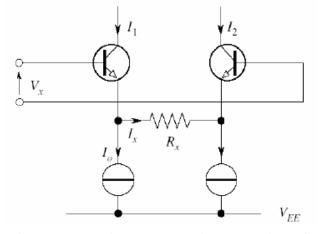

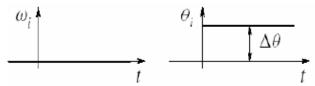

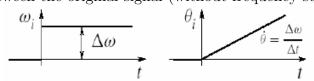

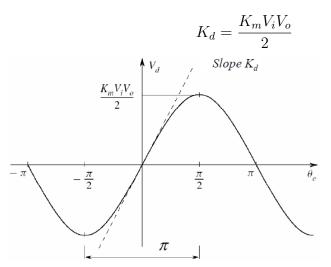

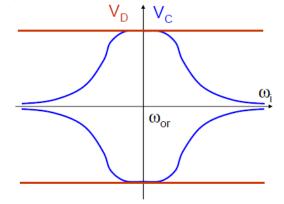

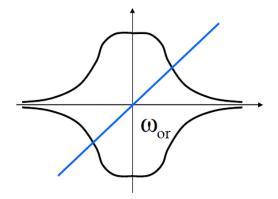

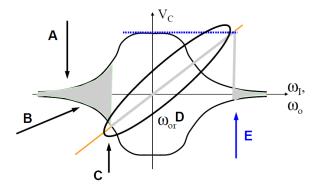

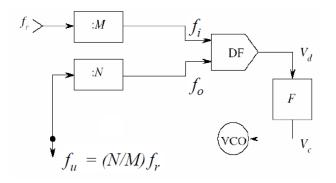

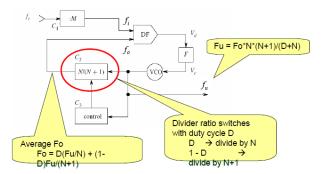

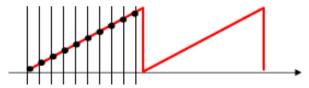

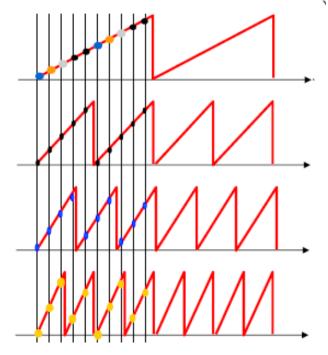

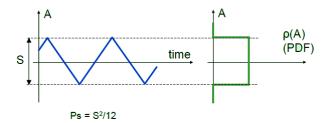

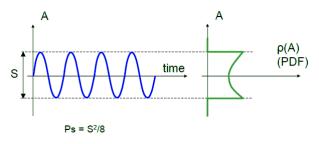

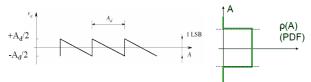

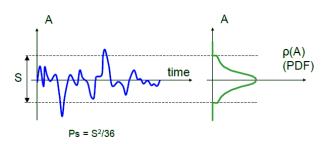

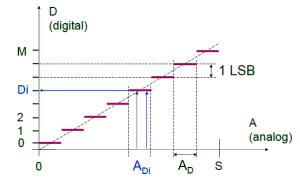

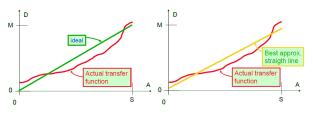

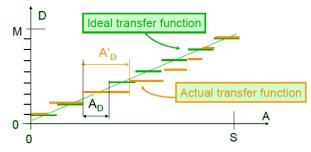

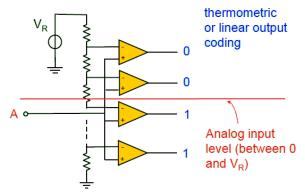

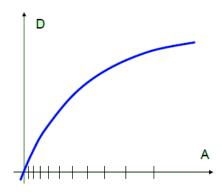

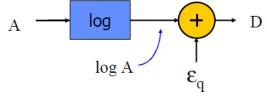

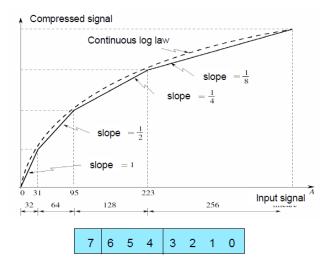

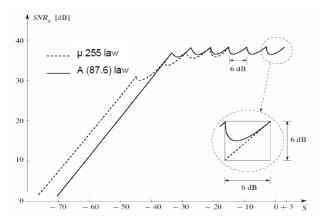

#### 3.0.3 Amplifier with emitter resistance